近日���,北京郵電大學(xué)EDA交叉團隊(集成電路學(xué)院趙康教授����、翟建旺特聘副研究員、計算機學(xué)院石川教授)在集成電路EDA領(lǐng)域國際頂會與學(xué)科競賽中取得多項突破��。團隊多項創(chuàng)新性研究成果被2025設(shè)計自動化會議(Design Automation Conference����,DAC)全文接收,并在中國研究生創(chuàng)“芯”大賽EDA精英挑戰(zhàn)賽中斬獲最高獎“菁英杯”�。

DAC會議是中國計算機學(xué)會推薦國際學(xué)術(shù)會議目錄中的A類國際頂會(CCF-A),與國際計算機輔助設(shè)計會議(ICCAD)�、歐洲設(shè)計自動化與測試大會(DATE)、亞洲及南太平洋設(shè)計自動化會議(ASP-DAC)并稱EDA領(lǐng)域四大國際學(xué)術(shù)會議�����,代表全球電子設(shè)計自動化(Electronic Design Automation���,EDA)研究的最高水平���。

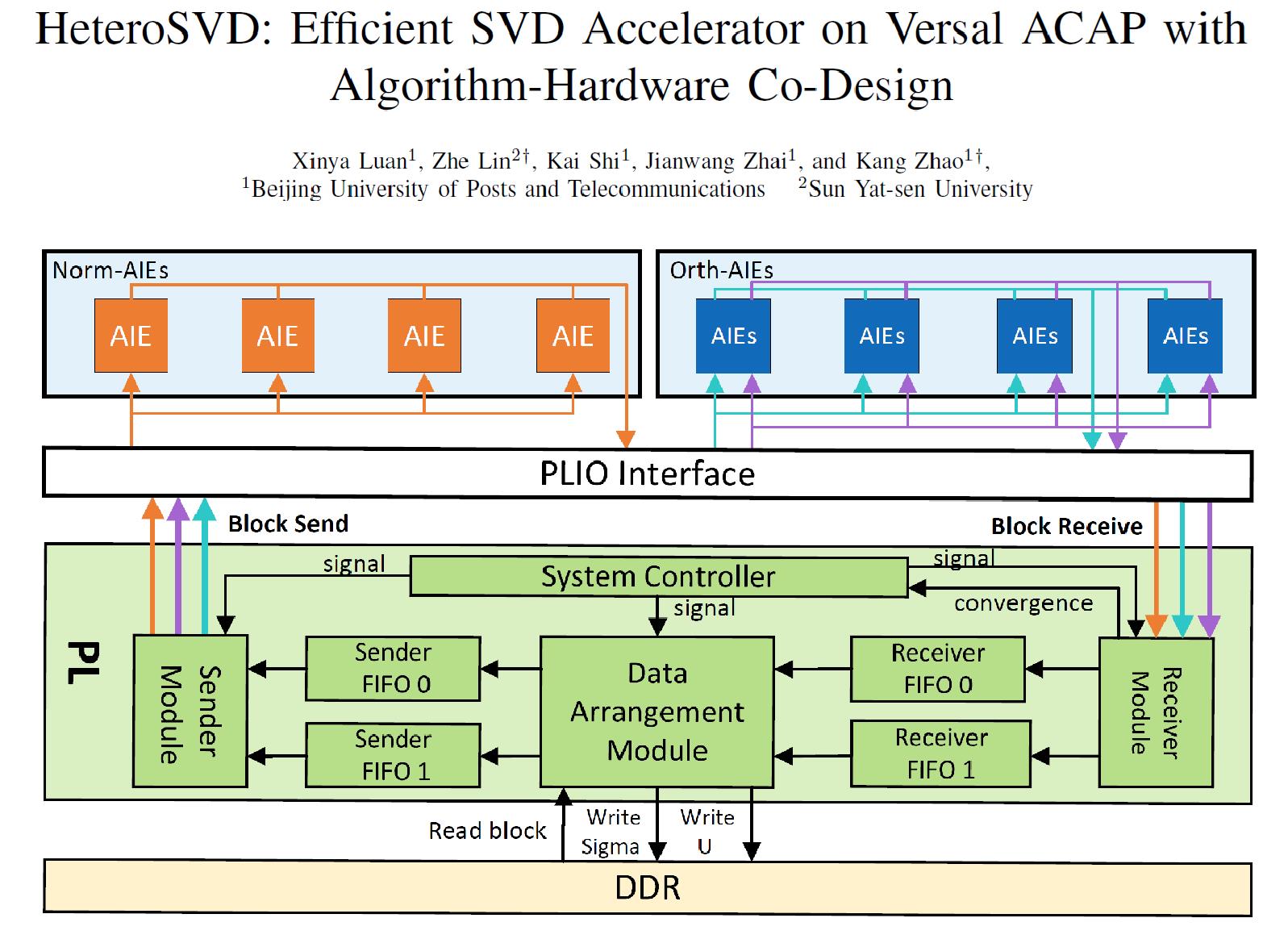

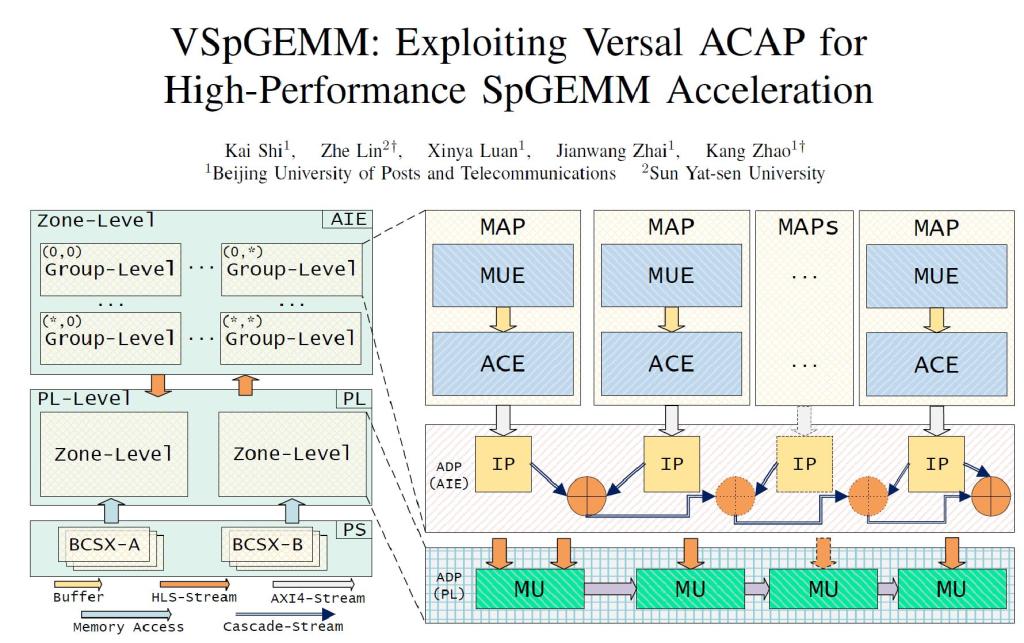

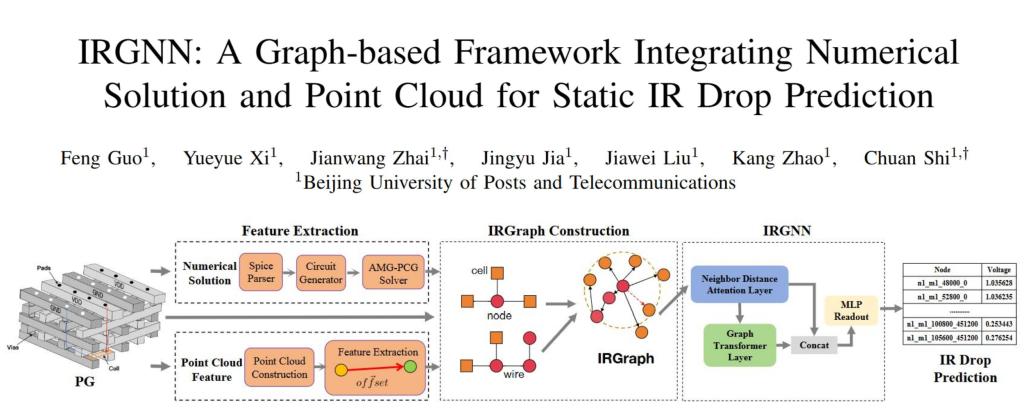

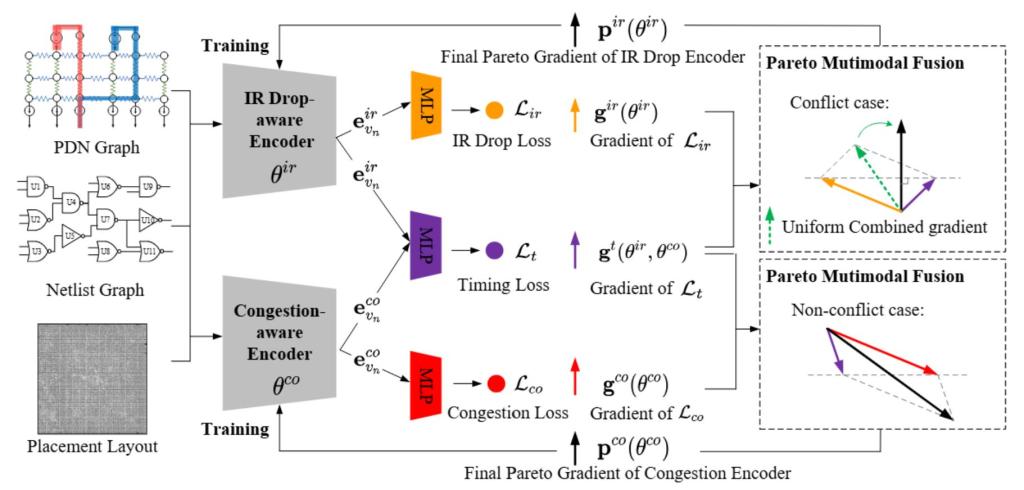

我校師生團隊刻苦鉆研,勇于攻關(guān)�,針對異構(gòu)可重構(gòu)芯片平臺的奇異值分解加速技術(shù)研究成果,面向異構(gòu)可重構(gòu)芯片平臺的兼具高性能����、低功耗的稀疏矩陣乘法加速方案相關(guān)成果�,基于圖神經(jīng)網(wǎng)絡(luò)的片上電源網(wǎng)絡(luò)的電壓降預(yù)測技術(shù)研究���,機器學(xué)習(xí)輔助芯片時序預(yù)測方面等多項創(chuàng)新性研究成果被2025設(shè)計自動化會議(Design Automation Conference,DAC)全文接收���。

|

|

| 奇異值分解的算法-異構(gòu)協(xié)同設(shè)計流程 |

通用稀疏矩陣乘算法在異構(gòu)可重構(gòu)芯片平臺的加速架構(gòu) |

|

|

| 基于圖結(jié)構(gòu)的靜態(tài)電壓降預(yù)測框架 |

基于多模態(tài)融合的布線前時序預(yù)測框架 |

北京郵電大學(xué)EDA團隊在中國研究生創(chuàng)“芯”大賽?EDA精英挑戰(zhàn)賽中共斬獲8項大獎���,包括菁英杯(最高獎之一)1項、一等獎1項�、三等獎1項、企業(yè)特別獎1項����、學(xué)術(shù)進取獎2項、優(yōu)秀指導(dǎo)教師獎2項����。

北京郵電大學(xué)EDA團隊將持續(xù)聚焦國家重大戰(zhàn)略需求,積極探索集成電路人才培養(yǎng)模式��,努力培養(yǎng)新時代集成電路產(chǎn)業(yè)高質(zhì)量人才�����,為國家突破技術(shù)封鎖貢獻關(guān)鍵力量。